library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity Comparator is

port(

CLK: IN std_logic;

RST: IN std_logic;

DATA: IN std_logic_vector(6 downto 0);

CNT: OUT std_logic_vector(2 downto 0)

);

end entity Comparator;

architecture Comparator_arch of Comparator is

-- Sem doplnte deklarace vnitrnich signalu pro komunikaci

-- mezi jednotlivymi bloky obvodu. Jako priklad je uveden

-- signal vystupu registru, na zaklade jehoz zmeny je

-- spousten proces cmp_proc (viz sensitivity list tohoto

-- procesu).

signal pre: std_logic_vector(6 downto 0);

signal cmpout: std_logic; --cystup comparatoru

---------------------------------------------------------

begin

-- Zde doplnte kod procesu popisujiciho komparator.

cmp_proc: process(DATA, pre)

begin

if (pre > DATA) then --predchozi pismenko je vyssi nez soucasne

cmpout <= '1'; --ano

else

cmpout <= '0'; --ne

end if;

end process cmp_proc;

-- Zde doplnte kod procesu popisujiciho registr.

reg_proc: process(CLK, RST)

begin

if (RST = '1') then --asynchronni reset

pre <= "0000000"; --ascii ma 7 bitu

elsif (CLK'event and CLK = '1') then --nabezna hrana

pre <= DATA; --uloz vstup

end if;

end process reg_proc;

-- Zde doplnte kod procesu popisujiciho citac.

cnt_proc: process(CLK, RST)

variable RES: std_logic_vector(2 downto 0); --vysledek (RESult)

begin

if (RST = '1') then --asynchronni reset

RES := (others => '0');

elsif (CLK'event and CLK = '1' and cmpout = '1') then --nabezna hrana a komparator

RES := RES + 1; --plus 1

end if;

CNT <= RES; --ulozeni vysedku

end process cnt_proc;

end architecture Comparator_arch;

library IEEE;

use IEEE.std_logic_1164.all;

entity TB_Comparator is

end entity TB_Comparator;

architecture TB_Comparator_arch of TB_Comparator is

constant period: time := 10 ns;

component Comparator is

port(

CLK: IN std_logic;

RST: IN std_logic;

DATA: IN std_logic_vector(6 downto 0);

CNT: OUT std_logic_vector(2 downto 0)

);

end component Comparator;

-- Vnitrni signaly test benche

signal clk: std_logic := '0';

signal rst: std_logic := '1';

signal data: std_logic_vector(6 downto 0);

signal cnt: std_logic_vector(2 downto 0);

begin

-- Sem doplnte instanci komponenty Comparator a namapujte

-- jeho vstupy a vystupy na vnitrni signaly test benche.

uut: Comparator

port map (

CLK => clk,

RST => rst,

DATA => data,

CNT => cnt

);

---------------------------------------------------------

clk <= NOT clk after period / 2;

TB_proc: process

begin

-- Sem doplnte prirazeni testovacich dat na vstupy obvodu.

-- Pro inspiraci je uvedena deaktivace resetu po uplynuti

-- doby k nabezne hrane hodin a vzorove prirazeni ASCII

-- hodnoty znaku X na datovy vstup obvodu. Povsimnete si,

-- ze v deklaracni casti test benche byl reset implicitne

-- nastaven na hodnotu '1'.

wait until clk'event AND clk = '1';

rst <= '0'; --odresetujeme

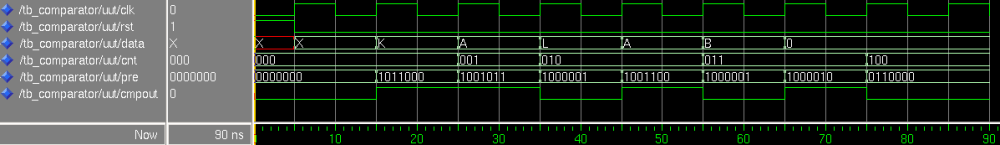

-- X K A L A B 0 0

-- 1011000 1001011 1000001 1001100 1000001 1000010 0110000 0110000

data <= "1011000"; --X

wait until clk'event AND clk = '1';

data <= "1001011"; --K

wait until clk'event AND clk = '1';

data <= "1000001"; --A

wait until clk'event AND clk = '1';

data <= "1001100"; --L

wait until clk'event AND clk = '1';

data <= "1000001"; --A

wait until clk'event AND clk = '1';

data <= "1000010"; --B

wait until clk'event AND clk = '1';

data <= "0110000"; --0

wait until clk'event AND clk = '1';

data <= "0110000"; --0

wait until clk'event AND clk = '1';

wait; --stuj

---------------------------------------------------------

end process TB_proc;

end architecture TB_Comparator_arch;