Obsah

Tahák

StateCharts

- Rozšíření

nedeterministickéhoKA - Synchronní komunikační mechanizmus

- Přechod na základě detekce události

reset

Diskrétní události

- Globální čas

- Událost kdykoliv asynchronně

- Výpočet daného bloku

v nanosekundách

Codesign konečné automaty

- Kombinace

nedeterministickýchkonečných automatů a diskrétních událostí - Lokálně synchronní a globálně asynchronní

- Neblokující buffery s konečnou velikostí – lze je přeplnit

VLIW

- Více funkčních jednotek

- Load/store architektura

Souběžnost řízená tokem dat

- Datové závislosti mezi operandy

Behaviorální hierarchie

- Dekompozice popisu chování úlohy

- Konec = výpočet všech podúloh v dané hierarchii

Komunikace

- Čtení sdíleného média

- Zprávy přes abstraktní kanály

Synchronizace

- Souběžně probíhající úlohy

- Společné hodinové signály

SpecCharts

- Program state machine

- Sdílená paměť a zasílání zpráv

- Přechody po ukončení stavu, nebo vyjímka

Rozdělování

- Exponenciální časová složitost

Univerzální standardní modelovací jazyk

- Neexistuje

- Překlad front-end → standardní

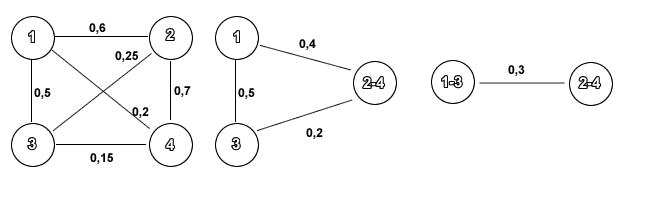

Hierarchický clustering

- Průměr hran do kříže1)

Stupeň využití

- Slack je zbytek do celého clocku (operace, která trvá 1,1 CLK má slack 90 %).

- Pak se jen vynásobí slacky počty operací a sečte se to.

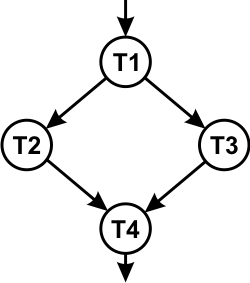

Doba výpočtu

Cílem je nejmenší doba výpočtu.2)

| Komponenta | Počet | Cena | Doba výpočtu | |||

|---|---|---|---|---|---|---|

| T1 | T2 | T3 | T4 | |||

| MIPS | 1 | 150 | 4 | 2 | ||

| DSP | 1 | 90 | 20 | 15 | 30 | |

| FPGA | 1 | 210 | 11 | 9 | ||

- Proč u T2 a T3 právě 11 a 15? Protože 11 + 15 < 20 + 9.

- A proč ne 11 a 9? Protože max(11, 15) < 11 + 9, no a taky proto, že máme jen jeden FPGA.

Doba výpočtu = 4 + max(11, 15)3) + 2 = 4 + 15 + 2 = 21

Cena = MIPS4) + DSP + FPGA = 150 + 90 + 210 = 450

Fidelity

Uděláš si dvojice ze všech možných kombinací odhadů a měření (odhad s odhadem, měření s měřením). Pak se koukneš, jestli jsou stejná znaménka nerovnosti u dvojic odhadu a měření, a výsledná fidelity je správně/dvojic.

| A | B | C | D | |

|---|---|---|---|---|

| E | 8 | 4 | 2 | 1 |

| M | 7 | 3 | 4 | 2 |

- E(A) > E(B); M(A) > M(B) ✔

- E(A) > E(C); M(A) > M(C) ✔

- E(A) > E(D); M(A) > M(D) ✔

- E(B) > E(C); M(B) < M(C) ✘

- E(B) > E(D); M(B) > M(D) ✔

- E(C) > E(D); M(C) > M(D) ✔

5/6 = 83 %

Struktury

| AND | OR | Struktura |

|---|---|---|

| Fixní | Programovatelné | ROM |

| Programovatelné | Programovatelné | PLA |

| Programovatelné | Fixní | PAL |

Amdahlův zákon

Speedup = (sekvenční + paralelizovatelné) / (sekvenční + (paralelizovatelné / stupeň urychlení))

40 % operací se podařilo urychlit dvojnásobně: 1 / (0,6 + (0,4/2)) = 1 / 0,8 = 1,25